输入输出系统

概述

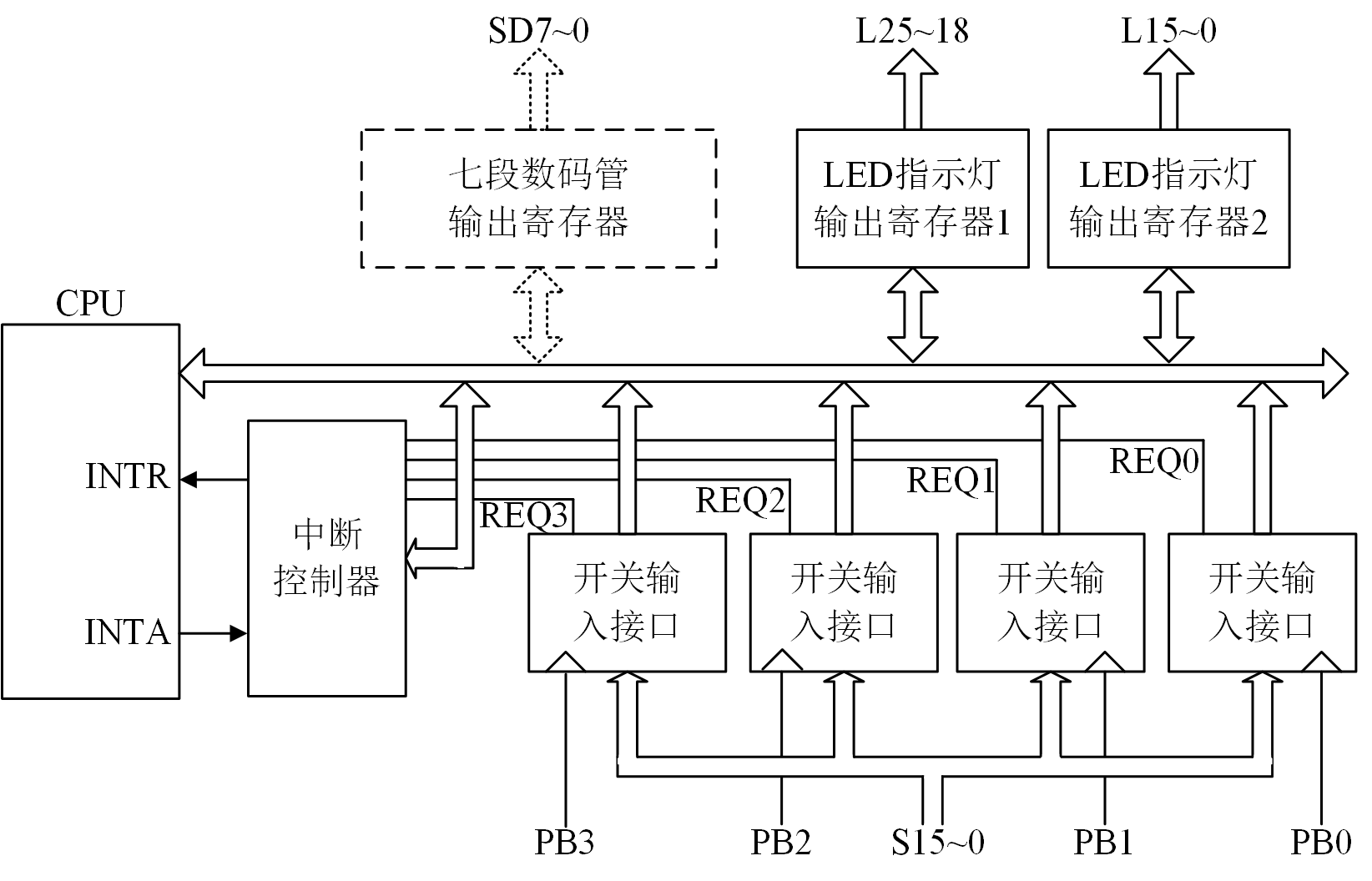

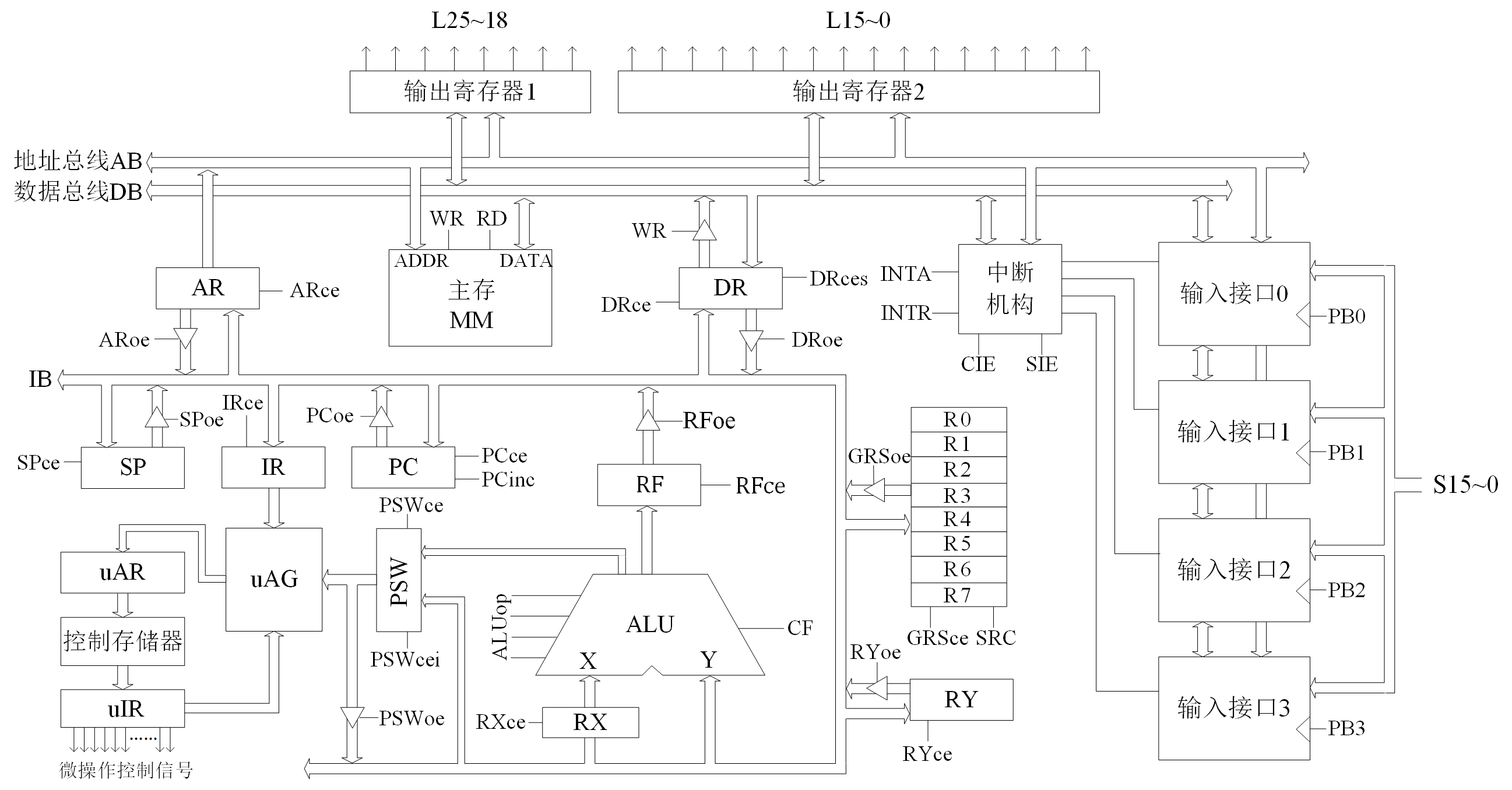

输入输出系统设计了4个输入接口,2个输出接口;还可扩充其它接口,如七段数码管的输出接口,如图 1。

| 接口地址 | 有效位数 | 名称 | 说明 |

|---|---|---|---|

FF00H |

4 |

中断屏蔽寄存器 |

对应4个中断源的屏蔽位,置1表示屏蔽 |

FF01H |

8 |

输出数据寄存器1 |

接指示灯L[25:18] |

FF02H |

16 |

输出数据寄存器2 |

接指示灯L[15:0] |

FF03H |

4 |

输入状态寄存器 |

对应4个输入接口的状态位 |

FF04H |

16 |

输入数据寄存器0 |

由按键PB0将开关S15~S0数据打入 |

FF05H |

16 |

输入数据寄存器1 |

由按键PB1将开关S15~S0数据打入 |

FF06H |

16 |

输入数据寄存器2 |

由按键PB2将开关S15~S0数据打入 |

FF07H |

16 |

输入数据寄存器3 |

由按键PB3将开关S15~S0数据打入 |

另外,为了与JUC-II兼容,保留了JUC-II的输入接口地址,见表 2 。虽然输入数据寄存器1~4中的每个寄存器分别有JUC-3的接口地址和JUC-II的接口地址,但硬件寄存器是同一个。JUC-II有4个状态寄存器,每个状态寄存器只有1位,对应一个输入接口;而JUC-3用一个状态寄存器的4位对应4个输入接口的状态,能够更高效地查询输入接口的状态。同样,状态寄存器的硬件只有一个,JUC-3和JUC-II只是接口地址不同。

| 接口地址 | 有效位数 | 名称 | 说明 |

|---|---|---|---|

FF08H |

16 |

输入数据寄存器0 |

由按键PB0将开关S15~S0数据打入 |

FF09H |

1 |

输入状态寄存器0 |

为1表示输入数据寄存器0有新数据 |

FF0AH |

16 |

输入数据寄存器1 |

由按键PB1将开关S15~S0数据打入 |

FF0BH |

1 |

输入状态寄存器1 |

为1表示输入数据寄存器1有新数据 |

FF0CH |

16 |

输入数据寄存器2 |

由按键PB2将开关S15~S0数据打入 |

FF0DH |

1 |

输入状态寄存器2 |

为1表示输入数据寄存器2有新数据 |

FF0EH |

16 |

输入数据寄存器3 |

由按键PB3将开关S15~S0数据打入 |

FF0FH |

1 |

输入状态寄存器3 |

为1表示输入数据寄存器3有新数据 |

输入输出接口

输出接口

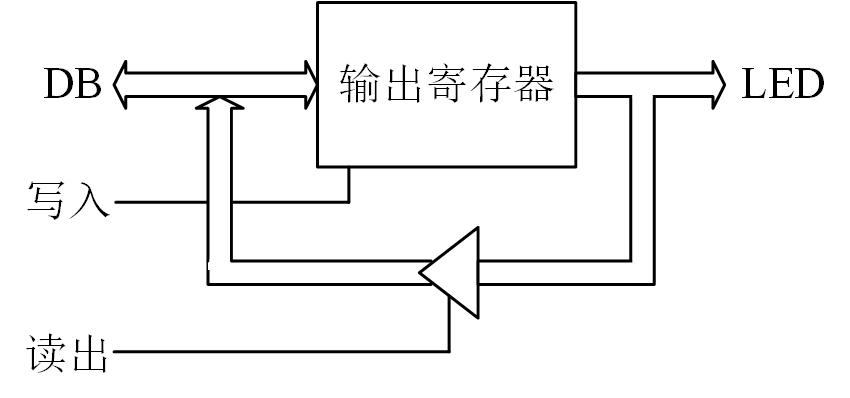

输出接口可以用来连接实验板上的LED指示灯,如虚拟实验板有36个可设置为红色或绿色的LED指示灯。模型机系统设计了2个数据寄存器作为输出接口, 1个8位接口寄存器的输出端连接到8个绿色LED,1个16位接口寄存器的输出端连接到16个红色LED,寄存器的输入端与系统数据总线相连,CPU不仅可以输出数据改变LED的状态,也可以从寄存器读回数据。输出接口的逻辑框图见图 2,其中“写入”由该接口的地址译码信号和主存写信号相与产生,“读出”由该接口的地址译码信号和主存读信号相与产生。

输入接口

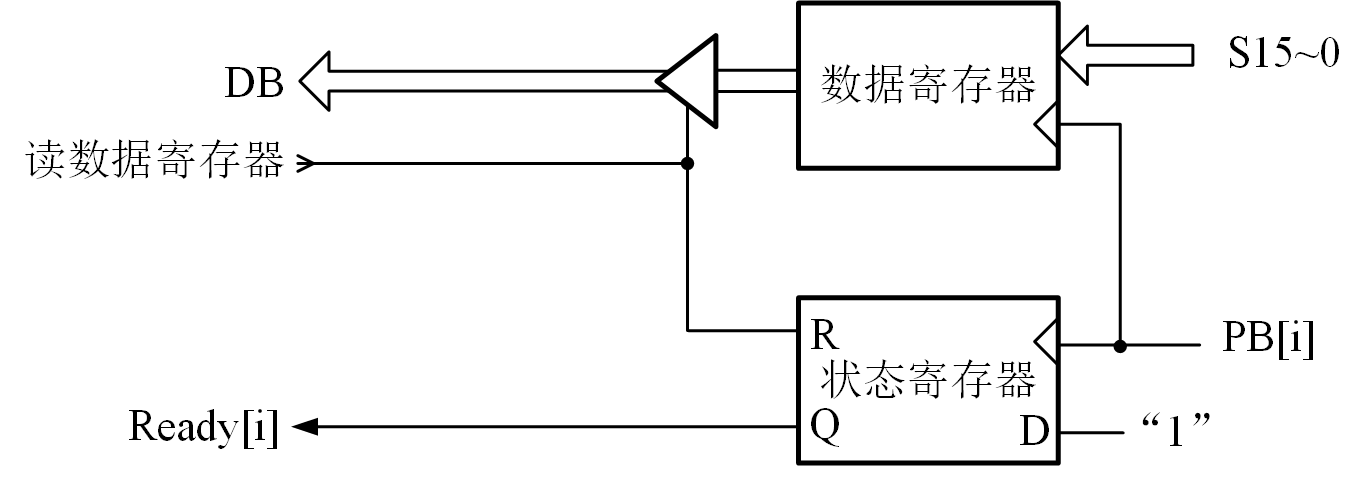

输入接口可以用来连接实验板上的拨动开关。如虚拟实验板有36个拨动开关和20个按键,模型机系统设计了4个输入接口连接到这些拨动开关和按键。每个输入接口含有1个16位的数据寄存器和1个1位的状态寄存器,如图 3所示。4个输入接口的时钟分别连接到虚拟实验板的PB0~PB3四个按键,而输入数据则共用16个拨动开关。

当按下某一个PB[i]按键时,将16个拨动开关作为数据打入该接口的数据寄存器,同时状态寄存器置1;状态寄存器的输出Ready[i]可以作为中断请求送给中断控制器;CPU读该接口数据寄存器时,数据寄存器读信号打开三态门,将数据寄存器的内容输出到DB数据总线,同时将状态寄存器清零。

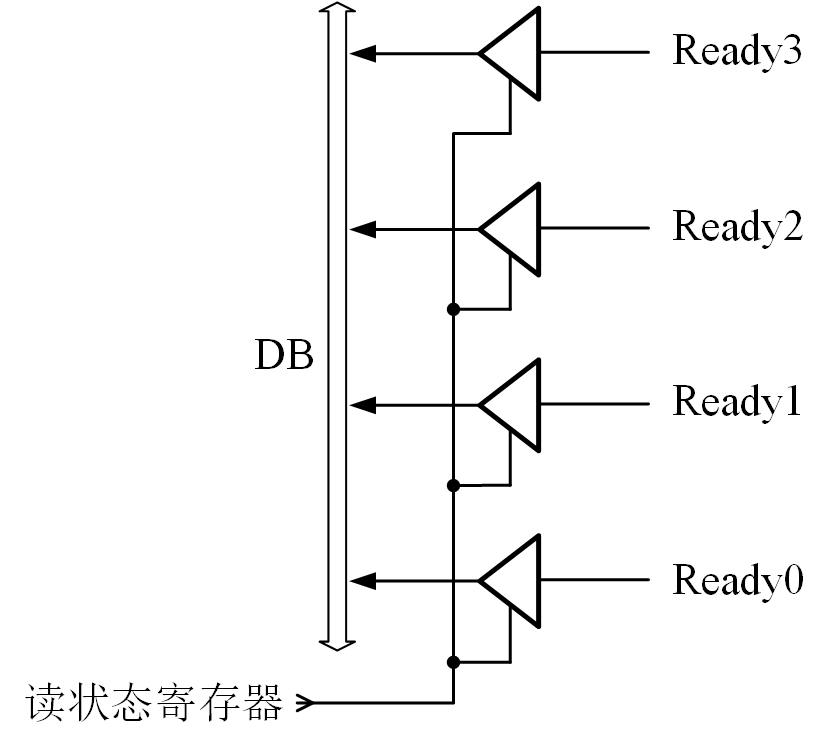

4个输入接口共用一个“状态寄存器”地址,由4个输入接口的状态位拼接成一个4位状态字,可以由CPU通过数据总线读出。如图 4,实际上这里并没有“寄存器”,只有三态缓冲器将4个输入接口中的状态寄存器的输出Ready[i]输出到数据总线上。

实战:查询方式输入

下面的程序是一个查询输入程序。它首先测试开关输入接口0的状态寄存器,如果有数据则读出开关输入接口的内容并送给红色LED接口显示。

ORG 0030H

ADDR1: TEST #0001H,FF09H ;测试状态寄存器0的最低位

JZ ADDR1 ;如果为0继续查询,否则顺序执行

MOV FF08H,FF02H ;将开关数据寄存器0的数据反映到红色LED

JMP ADDR1TEST指令与AND指令类似,只是逻辑与的结果不保存到目的操作数,但是影响PSW中的标志位。和CMP指令一样,编程时TEST指令通常与条件转移指令配合使用。

上面程序运行时如果没有输入数据,则循环测试状态寄存器;然后用拨动开关设置输入数据,按下PB0键将数据保存在输入寄存器中,此时测试状态寄存器为1,因此结束循环,执行MOV指令将输入数据寄存器0的值(开关输入的数据)显示在红色LED上。

中断

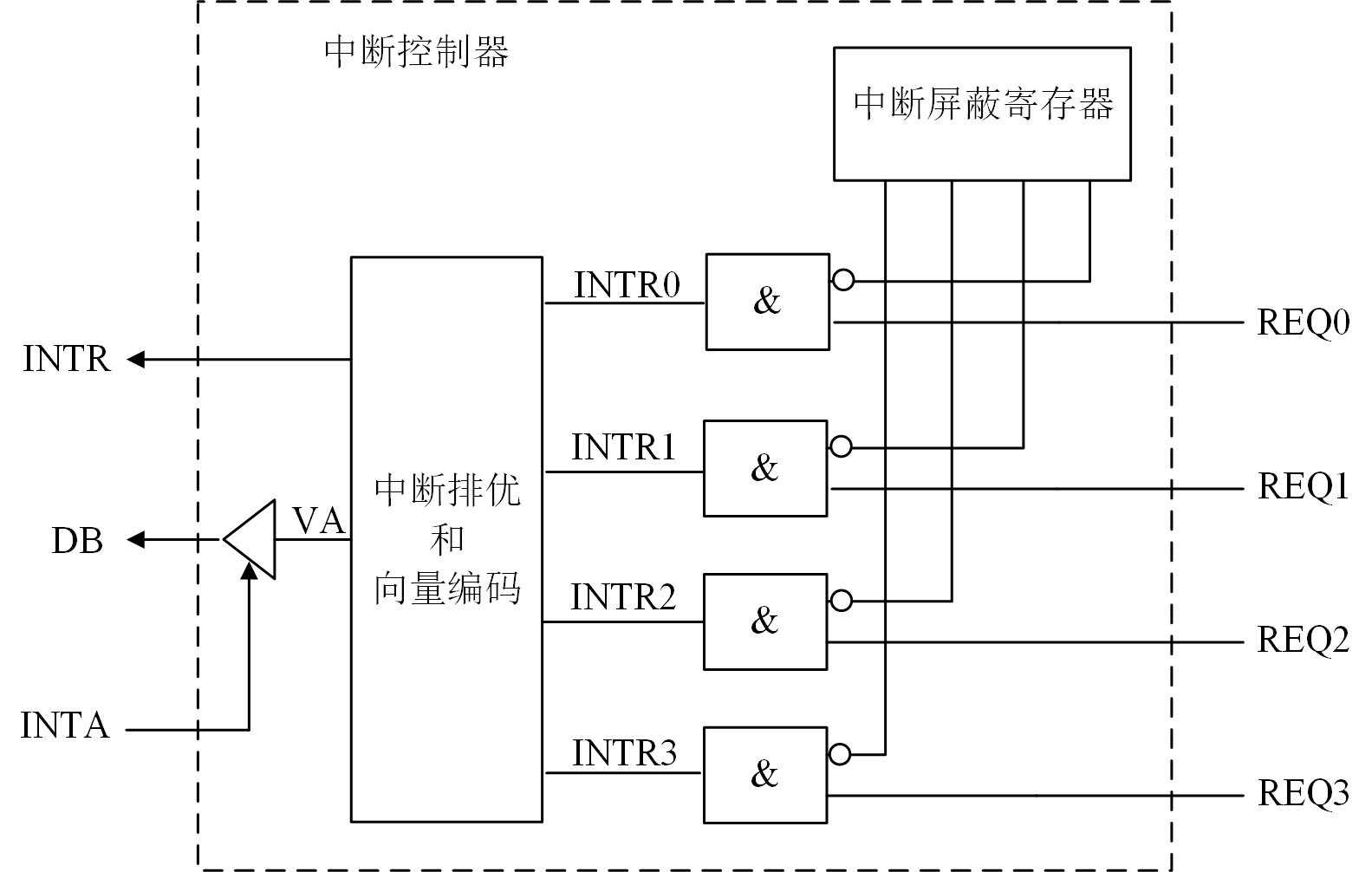

中断控制器

中断控制器的组成如图 5所示。中断屏蔽寄存器的地址是FF00H,因为模型计算机的外设与主存统一编址,故可以使用MOV指令访问FF00H地址实现对中断屏蔽寄存器写入或读出。

中断系统采用向量中断方式,当CPU响应中断时,发出INTA信号,将中断向量地址(向量编码)送到数据总线。中断向量表的首地址是0000H,每个中断向量占用一个存储单元,存放该中断服务程序的入口地址。向量地址与中断源的对应关系见表 3。

中断源 |

向量地址 |

INTR0 |

0000H |

INTR1 |

0001H |

INTR2 |

0002H |

INTR3 |

0003H |

支持中断的JUC-3扩展

数据通路和微命令的扩充

相应地需要增加一些微命令,扩充后的微指令格式见表 4,增加的微命令位于F7字段,其中PSWoe和PSWcei微命令控制图 6中PSW和内部总线之间的信息传递,INTA微命令控制图 5的向量地址向数据总线的信息传递。SIE(Set IE)和CIE(Clear IE)微命令控制允许中断触发器,SIE将其置1,即开中断,CIE将其清零,即关中断。

| F0:XXoe (3位) |

F1:XXce (3位) |

F2:ALU (4位) |

F3:PSW (3位) |

F4:S/D (1位) |

F5:SB (2位) |

F6:PC (1位) |

F7:Mem (3位) |

F8:BM (3位) |

F9: NA (9位) |

|---|---|---|---|---|---|---|---|---|---|

0:NOP |

0:NOP |

0:MOV |

0:NOP |

0:DST |

0:NOP |

0:NOP |

0:NOP |

||

1:PCoe |

1:PCce |

1:ADD |

1:PSWce |

1:SRC |

1:ARce |

1: PCinc |

1:RD |

||

2:DRoe |

2:IRce |

2:SUB |

2:DRces |

2:WR |

|||||

3:GRSoe |

3:GRSce |

3:AND |

3:DRce |

3:INTA |

|||||

4:RYoe |

4:RYce |

4:OR |

4:PSWoe |

||||||

5:ARoe |

5:RXce |

5:XOR |

5:PSWcei |

||||||

6:RFoe |

6:RFce |

6:SR |

6:SIE |

||||||

7:SPoe |

7:SPce |

7:SL |

7:CIE |

||||||

8:NOT |

|||||||||

9:INC |

|||||||||

A:DEC |

|||||||||

B:ADDC |

|||||||||

C:SUBB |

实战:中断相关的微程序设计与调试

1. 编写中断隐指令的微程序的微程序

中断隐指令需完成的操作:

(1)保护PC,即PC入栈;

(2)保护PSW,即PSW入栈;

(3)中断响应信号INTA有效,从数据总线读中断向量地址VA;

(4)根据VA,取出中断服务程序的入口地址,送PC;

(5)关中断。

注意微地址不要和以前的微程序冲突。

3. 编写中断返回指令(RETI)的微程序

中断返回指令需完成的操作与中断隐指令相对应,可以理解为是中断响应隐指令的逆操作,包括:

(1)恢复PSW,即栈顶单元弹出到PSW;

(2)恢复PC,即栈顶单元弹出到PC;

(3)开中断。

4. 调试微程序

用下面的主程序和中断服务程序验证上面编写的微程序。

ORG 0030H

MOV #0050H, 0000H

MOV #FFFEH, FF00H

EI

L1: NOP

NOT FF02H

JMP L1

ORG 0050H

MOV FF08H, FF02H

INC FF01H

RETI主程序中首先初始化中断向量表, INTR0的向量地址是0000H,用#0050H初始化0000H单元,表明INTR0(即PB0按键)中断服务程序的入口地址是0050H。FF00H是中断屏蔽寄存器的地址,用#FFFEH初始化中断屏蔽寄存器,表示允许INTR0中断请求,屏蔽其他中断请求。

0050H开始的是PB0按键的中断服务程序,该中断服务程序中,读取开关输入接口寄存器0的值,输出到红色LED输出接口寄存器中。

在开始执行后先用拨动开关设置数据,然后按PB0按键将开关状态保存到输入数据寄存器,同时发出中断请求,通过调试软件应能观察到中断请求信号REQ0已经产生,并且送给CPU的INTR为1;开中断指令执行后,通过调试软件应能观察到CPU的中断允许触发器IF为1。在NOP指令执行结束时检测到有中断请求并且允许中断,微程序转向执行中断隐指令。