基本时序逻辑电路

实验原理

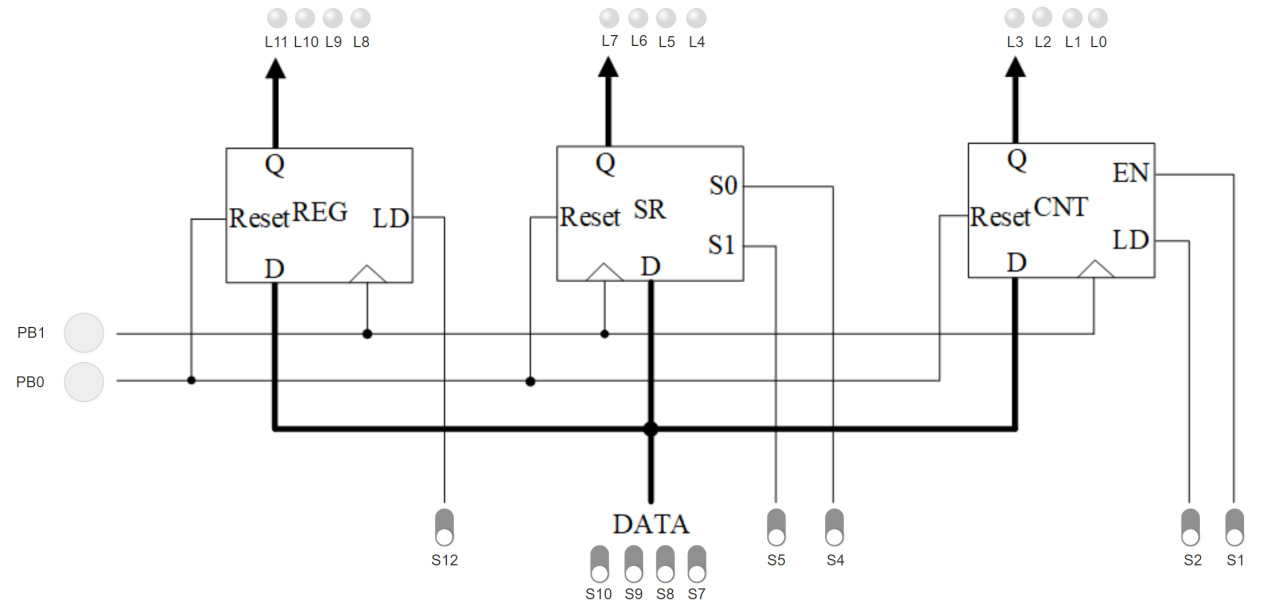

实验原理图如图 1。

图 1. 基本时序逻辑电路实验原理图

VirtualBoard模块代码见清单 1,它实例化了三个模块:数据寄存器REG、移位寄存器SR和计数器CNT。这三个模块共用输入数据DATA。数据寄存器的设计见清单 2,移位寄存器的设计见清单 3,计数器的设计见清单 4。数据寄存器和移位寄存器采用参数化的方法定义数据宽度,以便在以后的课程设计中能够复用这些代码,通过传递参数就可以将数据宽度拓展为16位。

清单 1. 虚拟实验板模块

`default_nettype none

module VirtualBoard (

input wire CLOCK, // 10 MHz Input Clock

input wire [19:0] PB, // 20 Push Buttons, logical 1 when pressed

input wire [35:0] S, // 36 Switches

output logic [35:0] L, // 36 LEDs, drive logical 1 to light up

output logic [7:0] SD7, // 8 common anode Seven-segment Display

output logic [7:0] SD6,

output logic [7:0] SD5,

output logic [7:0] SD4,

output logic [7:0] SD3,

output logic [7:0] SD2,

output logic [7:0] SD1,

output logic [7:0] SD0

);

/** The input port is replaced with an internal signal **/

wire RESET = PB[0];

wire CLK = PB[1];

wire CNTinc = S[1];

wire CNTce = S[2];

wire S0 = S[4];

wire S1 = S[5];

wire [3:0] DATA = S[10:7];

wire REGce = S[12];

/************* The logic of this experiment *************/

wire [3:0] REG_Q, SR_Q, CNT_Q;

// Instantiating DataReg Module

DataReg #(4) REG(.iD(DATA), .oQ(REG_Q), .Clk(CLK), .Load(REGce), .Reset(RESET));

// Instantiating Shifter Module

Shifter #(4) SR(.iD(DATA), .oQ(SR_Q), .Reset(RESET), .Clk(CLK), .S1(S1), .S0(S0));

// Instantiating Counter Module

Counter #(4) CNT(.iD(DATA), .oQ(CNT_Q), .Reset(RESET), .Clk(CLK), .Load(CNTce), .Enable(CNTinc));

/****** Internal signal assignment to output port *******/

assign L[3:0] = CNT_Q;

assign L[7:4] = SR_Q;

assign L[11:8] = REG_Q;

// assign L[15:12] = BUS;

endmodule清单 2. 数据寄存器

module DataReg

#(parameter N=4)

( output reg [N-1:0] oQ,

input wire [N-1:0] iD,

input wire Clk,

input wire Load,

input wire Reset

);

always @(posedge Clk or posedge Reset)

begin

if (Reset)

oQ = 0;

else if (Load)

oQ = iD;

end

endmodule清单 3. 移位寄存器

module Shifter

#(parameter N = 4)

(

output wire [N - 1: 0] oQ,

input wire [N - 1: 0] iD,

input wire Clk, Reset,

input wire S1, S0

);

reg [N-1:0] data;

always @(posedge Clk or posedge Reset)

begin

if (Reset)

data = 0;

else

case ({S1,S0})

2'b11: data = iD ;

2'b10: data = {oQ[N-2:0], 1'b0};

2'b01: data = {1'b0, oQ[N-1:1]};

default:data = data;

endcase

end

assign oQ = data;

endmodule清单 4. 计数器

module Counter

#(parameter WIDTH = 4)

(

input wire [WIDTH-1: 0] iD,

input wire Reset, Clk, Load, Enable,

output wire [WIDTH-1: 0] oQ

);

reg [WIDTH-1: 0] data;

always @(posedge Clk or posedge Reset)

begin

if (Reset)

data = 0;

else if (Load)

data = iD;

else if (Enable)

data = data + 1;

end

assign oQ = data;

endmodule