加减运算及特征标志

实验原理

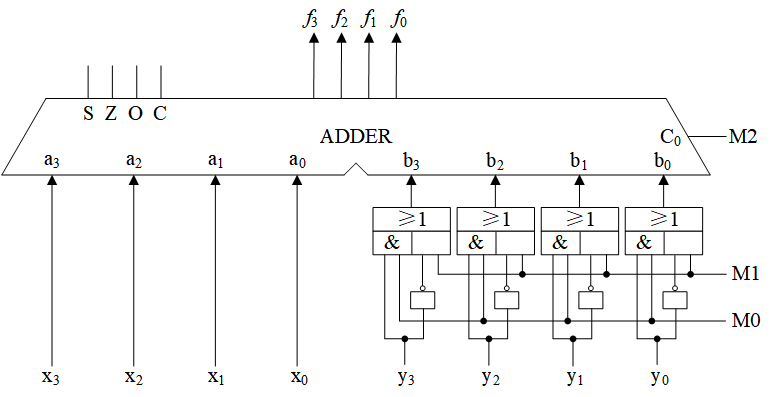

本实验设计的加减运算器以加法器为核心配合辅助逻辑实现加减运算,基本结构如图 1所示。

加法器的Verilog HDL设计见清单 1。FLAG是运算结果的标志,由S、Z、O、C构成,分别表示结果为负、运算结果为零、运算结果溢出、运算结果产生进位,根据特征标志的含义和生成方法补充完成 清单 1的①②③处的空白部分。

/** The input port is replaced with an internal signal **/

wire M2 = S[11];

wire M1 = S[10];

wire M0 = S[9];

wire [3:0] X = S[7:4];

wire [3:0] Y = S[3:0];

/************* The logic of this experiment *************/

wire [3:0] A,B,F;

wire C0;

wire sign, zero, overflow, carryOut;

assign A = X;

assign B = (Y & {4{M0}}) | (~Y & {4{M1}});

assign C0 = M2;

assign {carryOut,F[3:0]} = A + B + C0;

assign sign = ________; (1)

assign zero = ________; (2)

assign overflow = ________;(3)

/****** Internal signal assignment to output port *******/

assign L[3:0] = B[3:0];

assign L[7:4] = X[3:0];

assign L[12:9] = F;

assign L[26] = C0;

assign L[21:18] = {sign, zero, overflow, carryOut};预习要求

-

理解实验原理

根据实验原理分析各种运算对应的控制信号,填入下表。

运算指令

运算功能

运算控制信号

M2

M1

M0

传送X(MOV)

F=X

加法(ADD)

F=X+Y

减法(SUB)

F=X-Y

加1(INC)

F=X+1

减1(DEC)

F=X-1

-

完成特征标志的生成代码

根据特征标志的含义和生成方法补充完成清单 1的①②③处的空白部分。

sign、zero、Overflow分别表示结果为负、为零、溢出标志位。

实验任务

验证图 1加减运算电路的各项功能(包括特征标志),记录实验数据,分析实验结果。可以验证以下几个方面。

加法运算结果的特征标志

设置M2~M0为加法运算,按下表步骤操作,观察加法运算的结果,填入下表,并写出计算数和结果的真值。

X |

Y |

F |

FLAG |

运算数和运算结果的真值 |

|||||

S |

Z |

O |

C |

视为无符号数 |

视为补码 |

||||

① |

1000 |

0001 |

1001 |

1 |

0 |

0 |

0 |

8+1=9 |

(﹣8)+1=﹣7 |

② |

1101 |

1100 |

|||||||

③ |

0100 |

0010 |

|||||||

④ |

0000 |

0000 |

|||||||

⑤ |

1111 |

0001 |

|||||||

⑥ |

0011 |

0101 |

|||||||

⑦ |

1100 |

1011 |

|||||||

⑧ |

1100 |

0101 |

|||||||

⑨ |

0011 |

1011 |

|||||||

⑩ |

1000 |

1000 |

|||||||

提示:为方便分析运算结果,可以事先列出负数的4位补码与真值的对应关系:

补码 |

1000 |

1001 |

1010 |

1011 |

1100 |

1101 |

1110 |

1111 |

真值 |

实验现象分析:

着重分析无符号数加法运算结果是否溢出是由CF反映还是由OF反映,带符号数(补码)加法运算是否溢出是由CF反映还是由OF反映。理解同样的二进制编码既可以看做带符号数也可以看做无符号数,加减运算电路没有不同。