单总线数据通路

实验原理

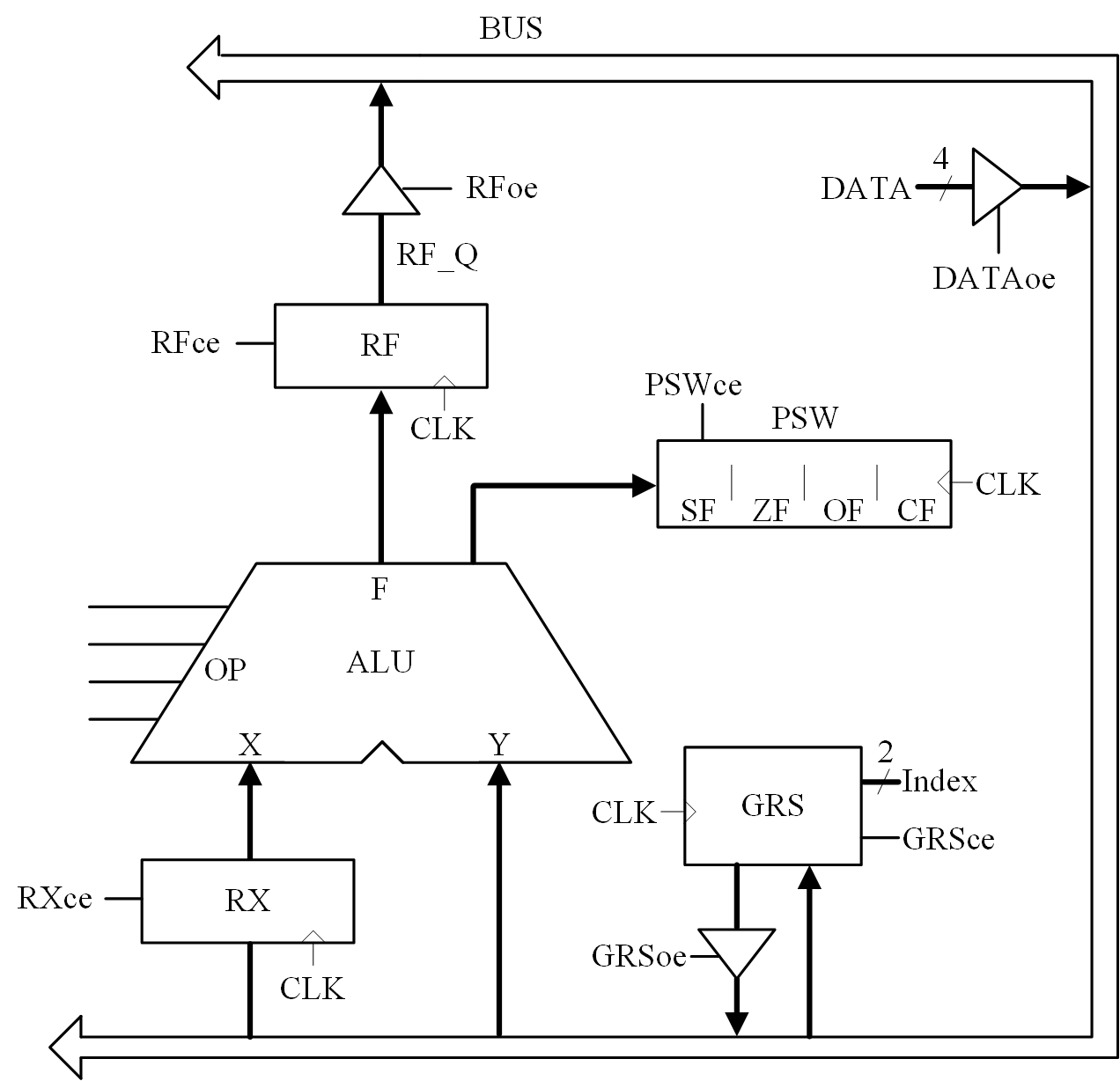

单总线数据通路实验原理如图 1所示。因为完成一次运算需要几个时钟周期,故也称为多周期数据通路。

图 1. 运算器数据通路

本实验的ALU在前面实验的基础上, 增加了控制信号的译码电路,将10种算术逻辑运算编码为4位的ALUop,下表给出了ALUop编码与运算功能的对应关系。

ALUop |

ALU运算 |

0000 |

传送X(MOV) |

0001 |

加法(ADD) |

0010 |

减法(SUB) |

0011 |

逻辑与(AND) |

0100 |

逻辑或(OR) |

0101 |

逻辑异或(XOR) |

0110 |

算术右移(ASR) |

0111 |

左移(SHL) |

1000 |

逻辑非(NOT) |

1001 |

加1(INC) |

1010 |

减1(DEC) |

通用寄存器组GRS(General Register Set)包含4个4位的通用寄存器R0~R3,用来存放参加运算的操作数和运算结果。

PSW存放ALU运算结果的特征标志。RX和RF是暂存器。图 1中没有标出RX、RF和PSW的RESET信号。

清单 1给出了虚拟实验板(VirtualBoard)模块的主体代码,其中实例化了ALU、GRS等各个子模块。两个核心模块ALU和寄存器组均已在前面的实验中完成,这里将它们封装成独立的模块。RX和RF是两个数据寄存器。PSW是一个4位的专用寄存器,用来保存运算结果的4个特征标志位。RX、RF和PSW均可用DataReg模块实例化。

清单 1. 数据通路

//各模块间连线信号

wire [3:0] BUS, RX_Q, F, RF_Q, GRS_Q;

wire [3:0] FLAG, PSW_Q;

//模块实例

ALU #(4) ALU_inst(.iOp(ALUop), .iX(RX_Q), .iY(BUS), .oF(F), .oFlag(FLAG), .Cin(PSW_Q[0]));

GRS #(4) GRS_inst(.iD(BUS), .oQ (GRS_Q), .Load(GRSce), .Clk(clk), .Index(INDEX));

DataReg #(4) RX_inst(.oQ(RX_Q), .iD(BUS), .Clk(clk), .Load(RXce), .Reset(reset));

DataReg #(4) RF_inst(.oQ(RF_Q), .iD(F), .Clk(clk), .Load(RFce), .Reset(reset));

DataReg #(4) PSW_inst(.oQ(PSW_Q), .iD(FLAG), .Clk(clk), .Load(PSWce ), .Reset(reset));

//三态缓冲器逻辑描述

assign BUS = RFoe ? RF_Q : 4'bzzzz;

assign BUS = GRSoe ? GRS_Q : 4'bzzzz;

assign BUS = DATAoe ? DATA : 4'bzzzz;