算术逻辑单元

实验原理

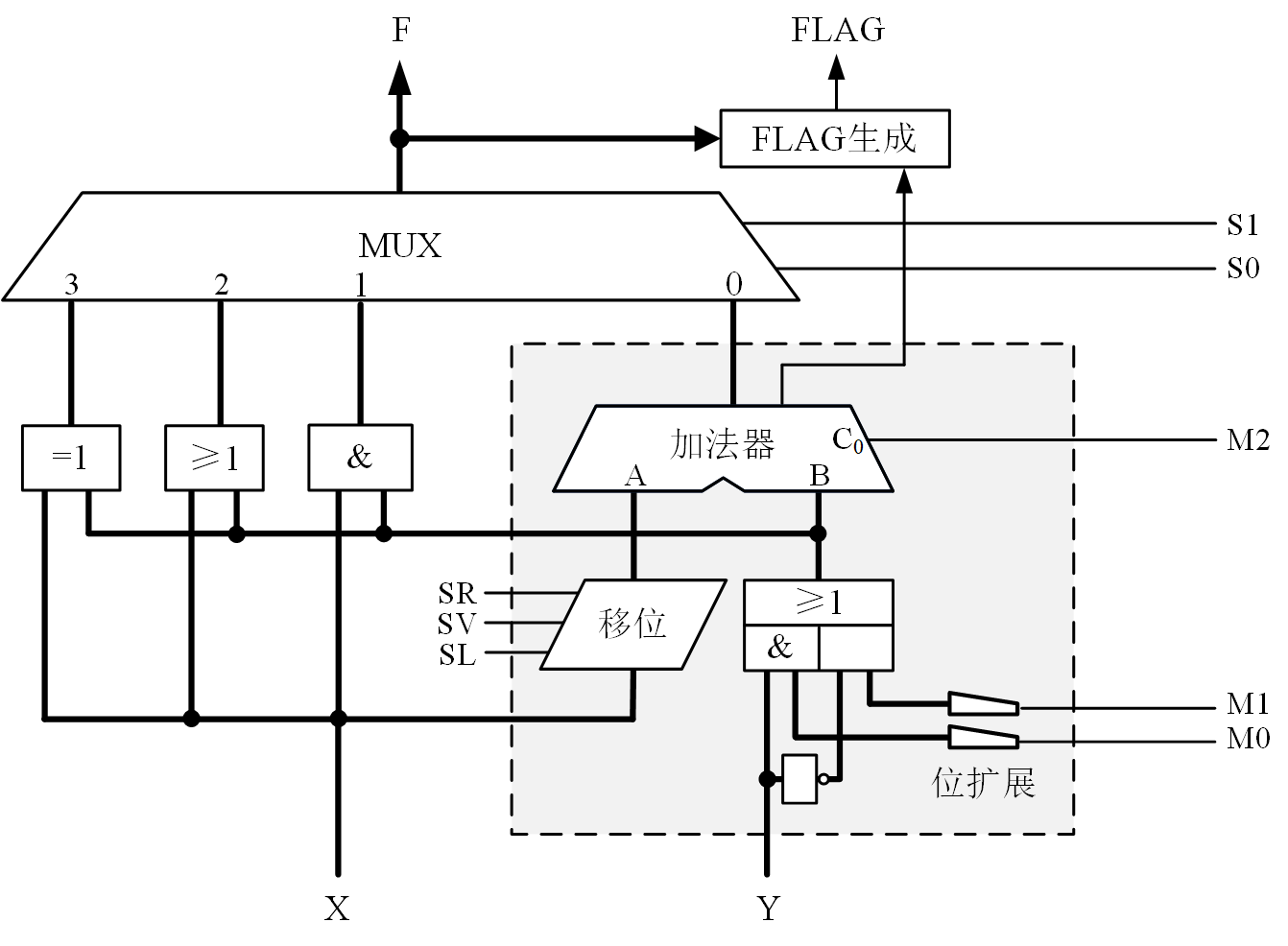

ALU是在加减运算电路的基础上, 扩充了移位运算和逻辑运算。实验电路结构如图 1。

图 1. ALU原理图

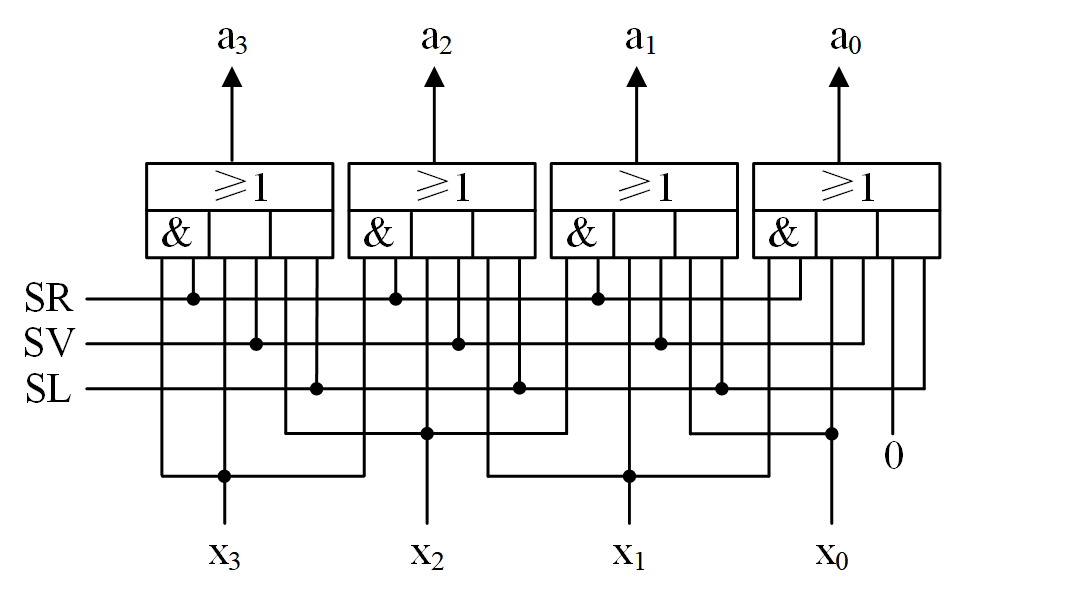

其中移位运算可以实现算术右移(SR)、逻辑左移(SL)和不移位(SV),电路结构如图 2。移位电路扩充在加法器的A输入端,通过控制M0、M1、M2均为0,使加法器的B和C0端均为0,从而将移位电路输出到加法器A端的数据传送到加法器的输出。

图 2. 移位运算电路

移位逻辑的Verilog描述见清单 1。

清单 1. ALU移位逻辑描述

assign A = X & {N{SV}} | {X[N-1],X[N-1:1]} & {N{SR}} | {X[N-2:0],1'b0} & {N{SL}}; 逻辑运算由与门、或门和异或门实现,并通过一个四选一多路器选择运算的功能。逻辑运算的一个运算数来自X,而另一个运算数并不是直接来自Y而是来自B,这是为了利用M0和M1均为1时B端为(1111)2的特性,从而可以用异或门实现对X的取反。

预习要求

-

理解电路原理

根据图 1 ALU原理图自己总结控制信号与运算功能的对应关系填写下表,其中ASR、SHL、INC、DEC和NOT要求均为单操作数运算,即Y的取值不会影响运算结果。

运算

功能描述

SR

SV

SL

M2

M1

M0

S1

S0

F=X

传送X(MOV)

F=X+Y

加法(ADD)

F=X-Y

减法(SUB)

F=X∧Y

逻辑与(AND)

F=X∨Y

逻辑或(OR)

F=X⊕Y

逻辑异或(XOR)

F=X/2

算术右移(ASR)

F=2X

左移(SHL)

F=

逻辑非(NOT)

F=X+1

加1(INC)

F=X-1

减1(DEC)

-

完成逻辑运算的HDL代码

将清单 2 VirtualBoard.sv中①②③处的空白部分填上逻辑运算的运算符。

清单 2. ALU运算逻辑描述always_comb begin case ({S1,S0}) 2'b00: result = A + B + C0; 2'b01: result = {1'b0, (X ___ B)}; (1) 2'b10: result = {1'b0, (X ___ B)}; (2) 2'b11: result = {1'b0, (X ___ B)}; (3) default: result = {(N+1){1'bx}}; endcase end1 逻辑与 2 逻辑或 3 逻辑异或