通用寄存器组

实验原理

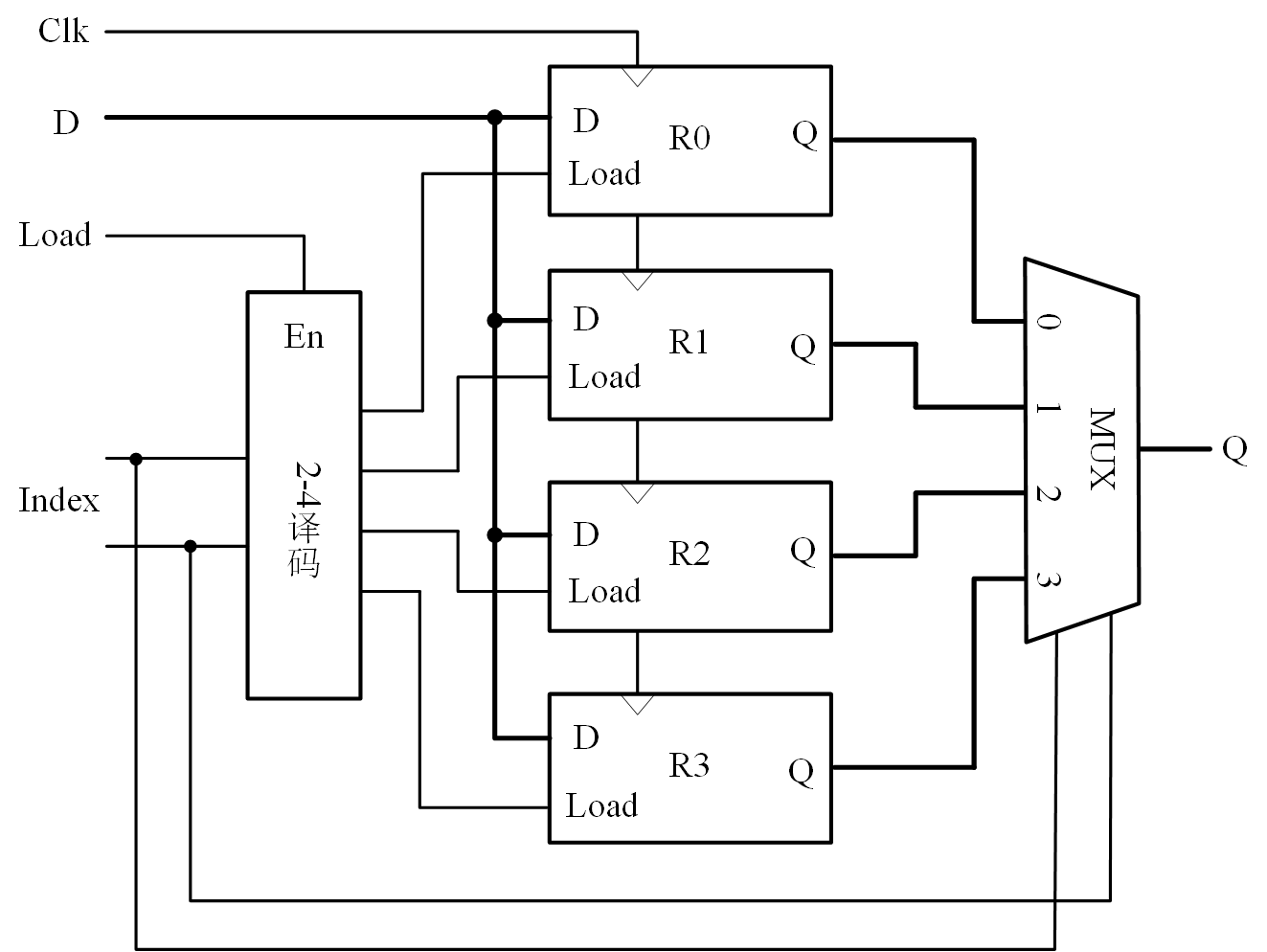

CPU内部通常包含若干个通用寄存器(Genral Register),以暂存参加运算的数据和中间结果。这些寄存器的集合就称为寄存器组(Register Set)。为方便访问其中的寄存器,对寄存器堆中的寄存器进行统一编码,称为寄存器号(Index)或者寄存器地址。图 1给出了一个通用寄存器组(GRS)的电路结构。

图 1. 单端口寄存器组的电路结构

它包含4个寄存器(R0~R1),每个寄存器存储4位二进制信息。寄存器组具有一个读数据端口Q和一个写数据端口D,但是地址端口Index是读写共用的,所以仍然属于单端口寄存器组。Load是地址译码器的使能信号,Load为1时,地址译码器根据Index选择某一个寄存器,使其在时钟到来时装入D端口的数据;当Load为0时,地址译码器的输出均为0,所有寄存器的内容均不会改变。HDL代码的主体结构见清单 1。

清单 1. 单端口寄存器组

localparam N = 4; // 寄存器字长

// 2-4 decode

logic load3, load2, load1, load0;

always_comb begin

if (Load)

case (Index)

2'b00: {load3, load2, load1, load0} = 4'b0001;

(1)

(2)

(3)

default: {load3, load2, load1, load0} = 4'bx;

endcase

else

{load3, load2, load1, load0} = 4'b0000;

end

// register instantiation

logic [N-1:0] R0_Q, R1_Q, R2_Q, R3_Q;

DataReg #(N) R0(.oQ(R0_Q), .iD(Data), .Clk(clk), .Load(load0), .Reset(1'b0));

(4)

(5)

(6)

// 4-1 MUX

logic [N-1:0] GRS_Q;

always_comb

begin

case (Index)

2'b00: GRS_Q = R0_Q;

(7)

(8)

(9)

default: GRS_Q = {N{1'bx}};

endcase

end预习要求

完成清单 1 VirtualBoard.sv模块中①~⑨处的HDL代码。