高速缓冲存储器

实验原理

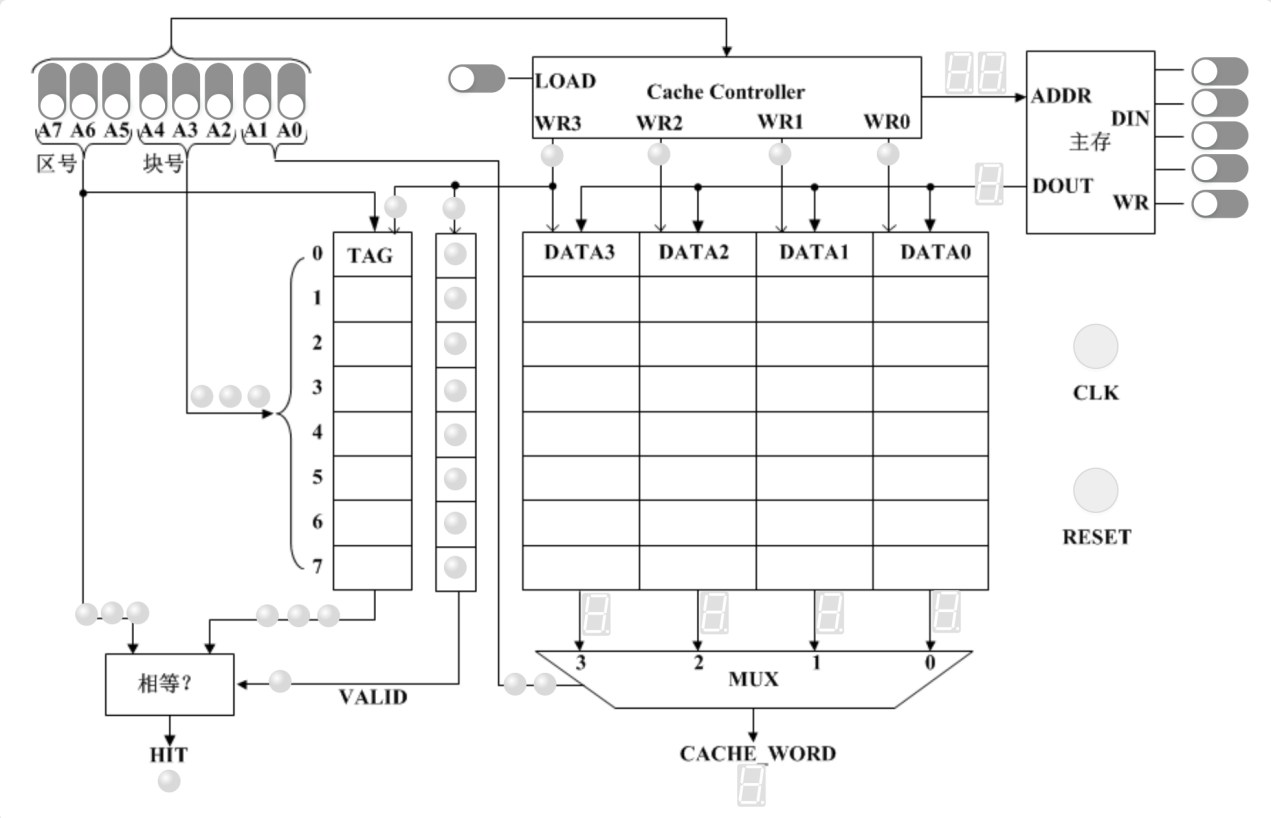

实验设计的存储器字长是4位。CACHE共32个字,采用直接映像,分8个块(BLOCK),也称作行(LINE),每块4个字(WORD);主存地址空间是256个字,按CACHE大小分区,即每区32字,共分8个区。实验原理如图 1。直接映像将地址分为三个部分:区号、块号、块内地址(也称字地址),用块号作为TAG和Cache行的地址。TAG存储器存放每个CACHE 行对应的主存块的区号,VALID存储器字长为1,复位时清0,主存块装入CACHE某一块时该块的VALID置1。

图 1. 直接相联映像方式CACHE结构

当访问主存某一单元时,以A7~A0中的块号为地址找到TAG存储器中的相应单元,并将该TAG单元内容与A7~A0中的区号比较一致并且VALID为1,表示Cache命中,此时用A7~A0中的块号选择Cache行,用字地址通过多路器MUX从一行的4个字中选择一个输出。如果TAG与A7~A0中的区号比较结果不一致或者VALID为0,说明不命中,即该单元不在Cache中,需要将主存该单元所在的块装入Cache。Cache Controller的WR信号有效时,在时钟CLK的作用下依次产生4个Cache字的写信号WR0~WR3,将读出的主存单元内容写入Cache。

主要设计代码见清单 1。

清单 1. cache组织

wire [2:0] field_TAG = AB[7:5];

wire [2:0] field_BLOCK = AB[4:2];

wire [1:0] field_WORD = AB[1:0];

wire [7:0] mm_addr;

//实例化主存储器

wire [3:0] mm_dout;

ram_with_init #(.ADDR_SIZE(8), .DATA_SIZE(4)) MM(.Q(mm_dout), .D(mm_din), .Addr(mm_addr), .WR(WR_MM), .Clk(clk));

//Cache控制器,产生主存地址和CACHE的字写入信号

wire WR0, WR1, WR2, WR3;

CacheController cc_inst (.Reset(reset), .Clk(clk), .iEnable(WR_CACHE), .iAddr(AB), .oAddr(mm_addr), .oWR({WR3,WR2,WR1,WR0}));

//实例化TAG存储器

wire [2:0] TAG;

wire WR_TAG = WR3;

ram #(.ADDR_SIZE(3),.DATA_SIZE(3)) TAG_inst(.Q(TAG), .DATA(field_TAG), .ADDR(___________), .WR(WR_TAG), .Clk(clk)); (1)

//VALID存储器

wire VALID;

wire [7:0] V_LED;

wire WR_VALID = WR3;

ram_valid VALID_inst(.VALID(VALID), .ADDR(____________), .RESET(reset), .WR(WR_VALID), .V_LED(V_LED)); (2)

//实例化CACHE存储器

wire [3:0] CACHE_WORD0,CACHE_WORD1,CACHE_WORD2,CACHE_WORD3;

ram #(.ADDR_SIZE(3),.DATA_SIZE(4)) DATA0(.Q(CACHE_WORD0),.DATA(mm_dout),.ADDR(field_BLOCK),.WR(WR0), .Clk(clk));

ram #(.ADDR_SIZE(3),.DATA_SIZE(4)) DATA1(.Q(___________),.DATA(_______),.ADDR(___________),.WR(WR1), .Clk(clk)); (3)

ram #(.ADDR_SIZE(3),.DATA_SIZE(4)) DATA2(.Q(___________),.DATA(_______),.ADDR(___________),.WR(WR2), .Clk(clk)); (4)

ram #(.ADDR_SIZE(3),.DATA_SIZE(4)) DATA3(.Q(___________),.DATA(_______),.ADDR(___________),.WR(WR3), .Clk(clk)); (5)

//实例化多路选择器模块

wire [3:0] CACHE_WORD;

MUX #(4) MUX_inst (.SEL(field_WORD), .A(CACHE_WORD0), .B(CACHE_WORD1), .C(CACHE_WORD2), .D(CACHE_WORD3), .MUX_OUT(CACHE_WORD));

//比较TAG存储器中读出的内容与当前地址寄存器AR中TAG字段的值是否相同,判断命中(HIT)

wire HIT;

assign HIT = VALID ? (_________ == ___) : 0 ; (6)预习要求

补充完成清单 1有数字标记处的代码。