中断电路

实验原理

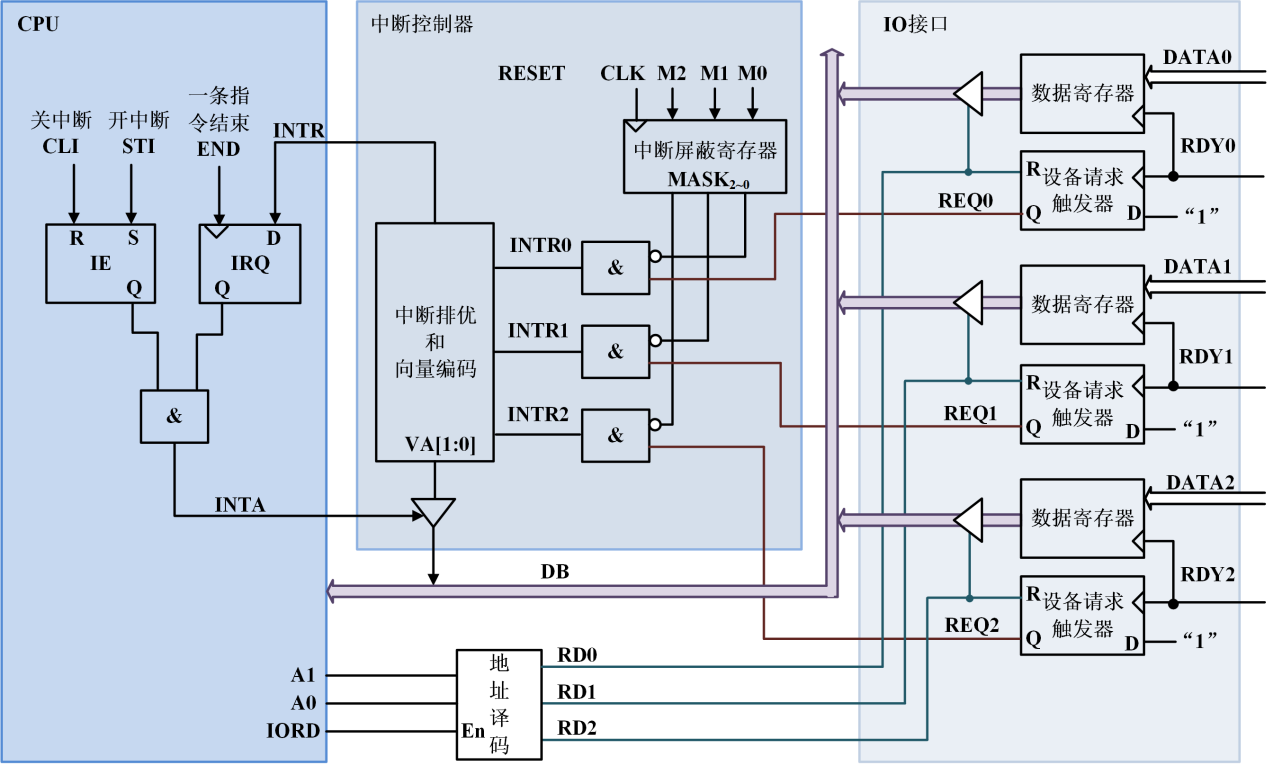

中断实验电路设计划分成CPU、中断控制器部分、IO接口三部分,实验电路结构如图 1。图中没有画出RESET信号,当RESET有效时,中断允许触发器、屏蔽寄存器和设备请求触发器清零。

(1)IO接口

设计了3个外部设备Device2,Device1,Device0,每个外部设备的IO接口都包含设备请求触发器和数据寄存器。

(2)中断控制器

中断控制器的设计包含中断屏蔽寄存器,中断信号生成,中断排优和向量编码。

(3)CPU

CPU部分包含中断允许触发器、中断请求触发器、中断响应产生。中断允许触发器设计为包含异步清零和异步置位功能的寄存器。中断请求和中断允许触发器的输出共同决定是否有中断响应信号产生。经过地址译码产生IO接口中数据寄存器的读信号。

主要设计代码见清单 1。

/** The input port is replaced with an internal signal **/

wire RESET = PB[0];

wire CLK = PB[1];

wire END_instruction = PB[2];

wire READY0 = PB[3];

wire READY1 = PB[4];

wire READY2 = PB[5];

wire M2 = S[14];

wire M1 = S[13];

wire M0 = S[12];

wire IORD = S[11];

wire A1 = S[10];

wire A0 = S[9];

wire STI = S[8];

wire CLI = S[7];

wire [3:0]DATA2 = S[23:20];

wire [3:0]DATA1 = S[19:16];

wire [3:0]DATA0 = S[3:0];

/************* The logic of this experiment *************/

wire [3:0] DB;

wire REQ0, REQ1,REQ2;

wire [3:0] Q_DATA0,Q_DATA1,Q_DATA2;

//地址译码器产生各接口的RD信号

logic [3:0] RD;

always_comb

begin

if (IORD)

case({A1,A0})

0: RD = 4'b0001;

1: RD = 4'b0010;

2: RD = 4'b0100;

3: RD = 4'b1000;

default: RD = 4'bxxxx;

endcase

else

RD = 4'b0000;

end

// device0的IO接口

DataReg #(1) REQUEST_inst0 (.iD(1'b1), .oQ(REQ0), .Clk(READY0), .Load(1'b1), .Reset(RD[0]));

DataReg #(4) DATA_inst0 (.iD(DATA0), .oQ(Q_DATA0), .Clk(READY0), .Load(1'b1), .Reset(1'b0));

assign DB = RD[0] ? Q_DATA0 : 4'bzzzz;

//device1的IO接口

DataReg #(1) REQUEST_inst1 (.iD(1'b1), .oQ(REQ1), .Clk(READY1), .Load(1'b1), .Reset(RD[1]));

DataReg #(4) DATA_inst1 (.iD(DATA1), .oQ(Q_DATA1), .Clk(READY1), .Load(1'b1), .Reset(1'b0));

assign DB = RD[1] ? Q_DATA1 : 4'bzzzz;

//device2的IO接口

DataReg #(1) REQUEST_inst2 (.iD(1'b1), .oQ(REQ2), .Clk(READY2), .Load(1'b1), .Reset(RD[2]));

DataReg #(4) DATA_inst2 (.iD(DATA2), .oQ(Q_DATA2), .Clk(READY2), .Load(1'b1), .Reset(1'b0));

assign DB = RD[2] ? Q_DATA2 : 4'bzzzz;

//中断屏蔽寄存器

wire [2:0] MASK;

DataReg #(3) MASK_inst (.iD({M2,M1,M0}), .oQ(MASK), .Clk(CLK), .Load(1'b1), .Reset(RESET));

//外设中断信号的产生

wire INTR0,INTR1,INTR2;

assign INTR0 = REQ0 & ~MASK[0];

assign INTR1 = REQ1 & ~MASK[1];

assign INTR2 = REQ2 & ~MASK[2];

//中断排优及向量编码

wire INTR; //送给CPU的中断请求信号

wire [1:0] VA;

VectorPriority Priority_inst (.IN({INTR2,INTR1,INTR0}), .OUT(VA), .INTR(INTR));

//CPU中断允许触发器

wire IE_Q;

IE #(1) IE_inst(.CLK(CLK),.RESET(CLI|RESET),.SET(STI),.D(IE_Q),.Q(IE_Q));

//CPU中断请求触发器

wire IRQ_Q;

DataReg #(1) IRQ_inst (.iD(INTR), .oQ(IRQ_Q), .Clk(END_instruction), .Load(1'b1), .Reset(RESET));

//CPU中断响应信号生成

wire INTA = IE_Q & IRQ_Q;

//向量地址输出到总线

assign DB = INTA ? VA : 4'bzzzz;预习要求

设计优先权排队和向量编码模块。完成清单 2有数字标记处的代码。

module VectorPriority ( //优先权排队

input wire [2: 0] IN,

output reg [1: 0] OUT,

output wire INTR

);

assign INTR = ; (1)

always @(IN)

begin

if (IN[0]) OUT = 2'b00;

(2)

(3)

else OUT = 2'bxx;

end

endmodule实验任务

1. 设备准备好数据,发出中断请求

通过拨动开关设置DATA0、DATA1、DATA2的输入数据,通过按键产生READY0、READY1、READY2的上升沿脉冲。观察并记录对应的REQ信号,分析结果是否正确。

接口(输入) |

接口(输出) |

结果分析 |

||||||||

DATA2 |

DATA1 |

DATA0 |

READY2,1,0 |

REQ2,1,0 |

||||||

初始 |

0000 |

0000 |

0000 |

0 |

0 |

0 |

0 |

0 |

0 |

设备没有中断请求 |

① |

—— |

—— |

0001 |

0 |

0 |

↑ |

||||

② |

—— |

0011 |

—— |

0 |

↑ |

0 |

||||

③ |

0111 |

—— |

—— |

↑ |

0 |

0 |

||||

④ |

—— |

—— |

—— |

0 |

0 |

0 |

||||

2. 中断屏蔽和中断排优

根据下表给出的输入信号设置中断屏蔽字,观察中断控制器的输出信号填入表格。(如果外设请求信号被意外清除,先参照步骤1产生设备中断请求)

输入 |

输出 |

结果分析 |

||||||||

RESET |

M2,1,0 |

CLK |

MASK |

INTR2 |

INTR1 |

INTR0 |

VA |

INTR |

||

① |

↑ |

—— |

—— |

|||||||

② |

0 |

001 |

↑ |

|||||||

③ |

0 |

011 |

↑ |

|||||||

④ |

0 |

111 |

↑ |

|||||||

⑤ |

0 |

000 |

↑ |

|||||||

实验结果分析:

(1)中断源能否向CPU发送中断请求由设备请求触发器(REQUEST)和中断屏蔽触发器(MASK)共同决定,分析INTR0、INTR1、INTR2的结果是否正确。

(2)如果多个中断请求同时发出,中断控制器根据中断源的优先级进行排队。第①行中,设备2、设备1和设备0的中断同时存在,中断控制器排优电路输出哪个设备的向量地址?第②行中,屏蔽了设备0的中断请求后,对于设备2和设备1中断,中断控制器排优电路输出哪个设备的向量地址?第③行中,又屏蔽了设备1的中断请求后,中断控制器排优电路输出哪个设备的向量地址?第④行中,屏蔽了所有的中断请求后,送给CPU的INTR和前面有什么不同?

(3)实验电路设计的中断响应的优先级顺序是怎样的?

3. 中断响应

先检查中断请求信号是否还在,如果没有,参照步骤1产生中断请求。为便于观察中断向量,屏蔽设备0的中断请求,开放设备1和设备2的中断请求,请参照步骤2第2行设置。下表中标题栏是斜体字的信号是输入信号,根据给出的值设置输入信号,将输出记录在表中。

中断控制器 |

CPU |

||||||||

INTR |

VA |

CLI |

STI |

END |

IE_Q |

IRQ_Q |

INTA |

DB |

|

当前 |

0 |

0 |

0 |

||||||

①开中断 |

0 |

1 |

0 |

||||||

②发中断应答信号 |

0 |

0 |

↑ |

||||||

③关中断 |

1 |

0 |

0 |

||||||

实验结果分析:

(1)《计算机组成原理》已经学过CPU响应中断的几个前提条件,分析第②行的结果,具体体现了哪些条件?在清单 1代码中是如何实现的?

(2)INTA有效时,数据总线DB上的内容是地址还是数据?CPU从数据总线上读取该信息后做什么?

(3)第③行,CLI产生关中断操作。关中断后,INTA信号如何变化?